Check for updates

## **Optics Letters**

## **One-volt silicon photonic crystal nanocavity modulator with indium oxide gate**

## Erwen LI, D QIAN GAO, SPENCER LIVERMAN, D AND ALAN X. WANG\*

School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, Oregon 97331, USA \*Corresponding author: wang@engr.orst.edu

Received 25 June 2018; revised 7 August 2018; accepted 9 August 2018; posted 14 August 2018 (Doc. ID 335973); published 11 September 2018

The ever-increasing global network traffic requires a high level of seamless integration between optical interconnect systems and complementary metal-oxide-semiconductor (CMOS) circuits. Therefore, it brings stringent requirements for future electro-optic (E-O) modulators, which should be ultracompact, energy efficient, high bandwidth, and in the meanwhile, able to be directly driven by the state-of-the-art CMOS circuits. In this Letter, we report a low-voltage silicon photonic crystal nanocavity modulator using an optimized metal-oxide-semiconductor (MOS) capacitor consisting of an In<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/p-Si stacked nanostructure. The strong light-matter interaction from the accumulated free carriers with the nanocavity resonant mode results in holistic improvement in device performance, including a high tuning efficiency of 250 pm/V and an average modulation strength of 4 dB/V with a moderate Q factor of  $\sim$ 3700 and insertion loss of  $\sim$ 6 dB using an ultrashort electrode length of only 350 nm. With 1 V driving voltage over a capacitive loading of only 13 fF, the silicon photonic nanocavity modulator can achieve more than 3 dB extinction ratio with energy consumption of only 3 fJ/bit. Such a low-voltage, low-capacitance silicon nanocavity modulator provides the feasibility to be directly driven by a CMOS logic gate for single-chip integration. © 2018 Optical Society of America

**OCIS codes:** (130.4110) Modulators; (130.5296) Photonic crystal waveguides; (200.4650) Optical interconnects; (230.5298) Photonic crystals; (250.0250) Optoelectronics; (250.7360) Waveguide modulators.

https://doi.org/10.1364/OL.43.004429

The exponentially growing global network traffic creates an unceasing driving force to upgrade the optical interconnect systems [1]. Silicon photonics offers the great potential to increase the integration level of photonics systems with complementary metal–oxide–semiconductor (CMOS) circuits, and ultimately monolithic integration that can significantly enhance the bandwidth of the optical interconnects and reduce the cost and energy consumption by orders of magnitude. To achieve this goal, it requires future silicon electro-optic (E-O) modulators,

the basic building block for optical communication systems, to be ultracompact, high bandwidth, and energy efficient. More importantly, the driving voltage of the modulator must be compatible with CMOS driving circuits, ideally directly driven by a CMOS logic gate. For example, a 32 nm CMOS technology node requires a peak-to-peak voltage swing around 0.9 V [2], and this value will further scale down with more advanced CMOS technology. However, because of the weak plasma dispersion effect of silicon, there is always a trade-off between the driving voltage and modulation length. Conventional Mach-Zehnder interferometer (MZI) based silicon E-O modulators occupy large footprints in order to operate in low voltage [3,4], which are not suitable for high density integration. On the other hand, microresonator based silicon modulators, such as microrings [5,6] or microdisk modulators [7,8], can operate in low voltage due to the high Q factor  $(10^4-10^5)$ of the resonator. But such high Q factor limits the RF operational bandwidth due to the long photon life time. For example, a Q factor above  $10^4$  will limit the RF bandwidth below 20 GHz. So for high-speed resonator based modulators, a moderate Q factor of a few thousand is desired. Besides, excessive Qfactor also requires heaters with precise feedback circuits to lock the operational wavelength.

In order to bypass the intrinsic limitations of silicon, people are seeking other active materials that can be integrated with the silicon photonics platform, such as graphene [9,10], transparent conductive oxides (TCOs) [11-14], and phase-change oxide materials [15]. Among them, TCOs, such as indium-tin oxide (ITO) and aluminum-zinc oxide, well known as transparent electrode materials in display and solar cell industries, have attracted escalating attention due to their strong plasma dispersion effect. The refractive index of TCO materials can experience unit order change by tuning the carrier concentration [16], and TCO also exhibits the unique epsilon-near-zero (ENZ) effect in the telecom wavelength window [17]. People have utilized the ENZ optical confinement effect to build electro-absorption modulators, such as hybrid plasmonic metal-oxide-semiconductor (MOS) modulators [11,12] and PlasMOStor [13]. However, it requires a relatively large driving voltage to accumulate enough carrier in order to turn the TCO materials into ENZ. In our previous work [14], we reported that by building a TCO/oxide/Si MOS capacitor on a photonic crystal nanocavity, we may take full advantage of the real part and imaginary part modulation of the optical permittivity from both TCO and Si, which enables us to achieve an efficient modulation in a sub-wavelength-scale active region. However, the tuning efficiency is limited by the small capacitance density due to the SiO<sub>2</sub> gate insulator layer. In this Letter, we report a low-voltage TCO-gated silicon photonic crystal nanocavity modulator using optimized MOS capacitor consisting of an indium oxide (In<sub>2</sub>O<sub>3</sub>)/HfO<sub>2</sub>/p-Si stacked nanostructure. Using the 10 nm thick high-k dielectric material,  $HfO_2$ , as the gate insulator layer greatly increases the capacitance density in the active region, bringing unprecedented energy efficiency. We experimentally demonstrate a high resonance tuning efficiency of 250 pm/V. The device exhibits an average modulation strength of 4 dB/V for a moderate Q factor of  $\sim$ 3700. The 3 dB driving voltage is reduced to less than 1 V on a 13 fF gate, which can be directly driven by CMOS logic gates without any additional signal amplification. Besides, the device also preserves the feasibility to scale down the driving voltage by reducing the thickness of the gate oxide layer. Since the active volume of our nanocavity modulator is 10-50× smaller compared with microring or microdisk modulators, our modulator should be more efficient in thermal tuning. Also the moderate Q factor makes the device quite tolerant to temperature variation, although a thermal heater may still be needed to lock the operational wavelength.

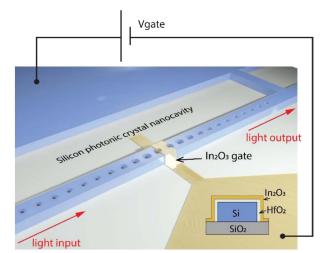

Figure 1(a) shows the schematic of the photonic crystal nanocavity E-O modulator. A photonic crystal nanocavity is created on a strip silicon waveguide 500 nm in width and 245 nm in height. Two tapered photonic crystal mirror segments are placed back to back, resulting in a zero-length cavity. Each mirror segment consists of 12 air holes with a period of 340 nm. The size of air holes is quadratically tapered from the edge to the center [18]. An  $In_2O_3/HfO_2/p$ -Si film stack is formed in the center of nanocavity, forming a MOS capacitor which is the active region of the modulator with cross sectional view shown in the Fig. 1(a) inset. Here, the p-Si performs as the semiconductor layer. Two silicon strips are placed 5  $\mu$ m away from the center on each side of the cavity, providing electrical connection between the silicon cavity and the silicon slab contacted with the metallic electrode. A 10 nm thick high-*k*

Fig. 1. 3D schematic of the photonic crystal nanocavity modulator. Inset: cross section schematic of the  $In_2O_3/HfO_2/p$ -Si film stack in the active region.

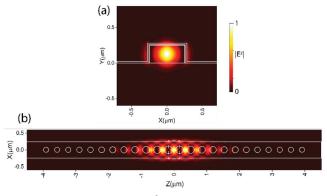

dielectric, HfO<sub>2</sub>, film serves as the gate oxide. On the top, a 20 nm thick  $In_2O_3$  film acts as the TCO gate electrode. Here, we choose In<sub>2</sub>O<sub>3</sub> as the TCO material instead of previously used ITO, because In<sub>2</sub>O<sub>3</sub> offers slightly higher mobility than ITO in our fabrication facility, which can potentially improve the plasma dispersion effect. The total length of the overlapping area is 350 nm. Compared with other high-Q resonators such as microrings and microdisks, a photonic crystal nanocavity has more confined mode volume [18,19]. We simulate the photonic crystal nanocavity modulator based on 3D finite-difference time-domain (FDTD) method. The nanocavity operates in the transverse-electric (TE) mode. The simulation shows an ultracompact mode volume of  $0.049 \ \mu m^3$  $(0.25 (\lambda/n)^3)$ , which is more than one order of magnitude smaller than the most compact microdisk resonator [20]. Figures 2(a) and 2(b) show cross sectional and top views of the optical mode profile of the TE cavity mode. The best tuning efficiency of the plasma dispersion effect happens when the carrier modulation happens near the region where the optical field has the maximum power [7]. In the photonic crystal nanocavity modulator, this corresponds to the center silicon region (~130 nm wide) between two photonic crystal segments. In our design, we chose the  $In_2O_3$  gating length to be slightly bigger than one period between air holes, mainly due to the consideration of fabrication tolerance. But it still gives us an ultrasmall active volume of  $V_a = 0.06 \ \mu m^3$ .

The active region of the photonic crystal nanocavity modulator is driven by a MOS capacitor. A negative bias applied on the  $In_2O_3$  gate produces free carrier accumulation at both the  $In_2O_3/HfO_2$  (electron) and the  $HfO_2/p$ -Si (holes) interfaces. We know that the permittivity change caused by the plasma dispersion is proportional to the change of free carrier concentration [14]. A MOS capacitor can easily provide a huge capacitance density using a thin high-k gate insulator layer. For example, a MOS capacitor with 10 nm HfO<sub>2</sub> gate oxide layer has a large capacitance density of 22.1 fF/ $\mu$ m<sup>2</sup>. In comparison, the capacitance density for the p - n junction with doping level of  $10^{18}$  cm<sup>-3</sup> is only ~1.5 fF/µm<sup>2</sup>. Especially for our photonic crystal nanocavity modulator, it is actually a 3D-MOS capacitor. Free carriers can accumulate at all the surrounding interfaces (side wall interfaces in four in-plane directions and the top interface). A large capacitance (C) can be achieved in a very small active volume  $(V_a)$ . We simulate the capacitance

**Fig. 2.** (a) Cross sectional  $|E^2|$  distribution in the center of the photonic crystal nanocavity ( $Z = 0 \ \mu$ m). (b)  $|E^2|$  distribution in the center plane of the photonic crystal nanocavity.

of the modulator through commercially available software (ANSYS HFSS) based on the finite element method. The simulation gives a gate capacitance of 13 fF, which corresponds to a capacitance over active volume ratio of  $C/V_a = 216$  fF/ $\mu$ m<sup>3</sup>.

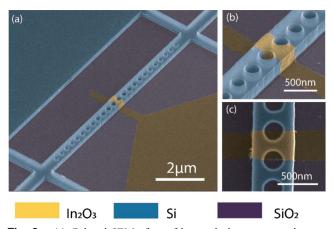

The modulator fabrication process starts with a *p*-type silicon-on-insulator (SOI) wafer with a silicon layer thickness of 250 nm and the buried oxide layer thickness of 3 µm. First, the SOI wafer is uniformly implanted with 34 keV B+ ions at a flux of  $2 \times 10^{13}$  ions cm<sup>-2</sup> to lightly dope the silicon layer and reduce the resistivity. Then the silicon waveguide, photonic crystal cavity, and grating couplers are patterned by diluted ZEP520A resist using electron beam lithography (EBL), followed by a reactive ion etching process to etch through the silicon layer. We found that the resonance peak of our fabricated device shifts to shorter wavelengths compared with the design value. The dimension of the actual fabricated device is 5% larger than the designed value as listed above. A 10 nm thick SiO<sub>2</sub> layer is then formed by thermal oxidation at 1000°C in order to smooth the etching surface (to improve the Q factor) and also activate the dopants. After etching the SiO<sub>2</sub> layer by buffered oxide etchant (BOE), a 10 nm thick HfO<sub>2</sub> is deposited using atomic layer deposition. Next, Al and Au electrode pads are patterned by contact photolithography, thermal evaporation, and lift-off processes, contacting with the Si and In<sub>2</sub>O<sub>3</sub> layers, respectively. Before metal evaporation, the overlapped HfO<sub>2</sub> layer is removed by BOE. The sample is then annealed at 475°C to form ohmic contact between Al and Si. Finally, the 20 nm  $In_2O_3$  gate layer is patterned by a second time EBL with ZEP resist followed by room-temperature RF sputtering and lift-off processes. Figures 3(a)-3(c) show the scanning electron microscopy (SEM) images of one fabricated device.

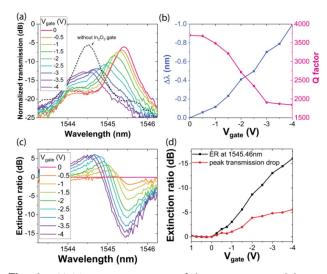

We perform optical and E-O modulation characterization of the device. Light is coupled into and out of the silicon waveguide through grating couplers from optical fibers with a 10° tilted angle. At the input side, a polarization-maintaining fiber is used to maintain the TE mode polarization controlled by a polarization controller. The output light is then coupled into an optical spectrum analyzer. During the E-O testing, a DC voltage is applied onto the top  $In_2O_3$  gate electrode while the bottom silicon waveguide is grounded. Figure 4(a) shows

**Fig. 3.** (a) Colored SEM of one fabricated photonic crystal nanocavity modulator. (b) Zoomed-in SEM of the MOS structure in the active region of the nanocavity modulator. (a) and (b) are taken with the sample tilted at  $45^{\circ}$ . (c) Top view SEM of the active region of the nanocavity modulator.

**Fig. 4.** (a) Transmission spectra of the nanocavity modulator at different bias voltages (solid lines) and before sputtering the  $In_2O_3$  gate (black dashed line). (b) Peak wavelength shift and Q factor as a function of applied bias. (c) Extinction ratio spectra at different bias voltages. (d) Extinction ratio at maximum efficiency wavelength (1545.46 nm) and the peak transmission reduction as a function of the applied voltage.

the plots of the transmission spectra at different applied bias voltages. The spectra are normalized to a straight Si waveguide with the same crossing strips as the reference. When no bias applied, a transmission peak with a relative high Q factor of 3700 is observed at 1545.39 nm. The insertion loss at peak wavelength is  $\sim 6$  dB, which is mainly caused by fabrication errors and waveguide surface roughness. Compared with the transmission spectrum before sputtering the In<sub>2</sub>O<sub>3</sub> gate [black dashed curve in Fig. 4(a)], the effect of the  $In_2O_3$  gate on the Q factor is negligible. We should point out that the current moderate Q factor of our device is majorly limited by our fabrication errors. With an optimized process, higher Q factor and lower insertion loss should be achievable [21]. As we apply the bias voltage on the In2O3 gate, electrons and holes start to accumulate at the In<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> and Si/HfO<sub>2</sub> interfaces, respectively. The accumulated carriers induce modulation to both the real part and the imaginary part of the optical permittivity, and both contributes to the E-O modulation. The real part variation of the permittivity causes the resonance peak to blueshift to shorter wavelength. By increasing the applied voltage from 0 to -4 V, the resonant peak blueshifts by 1 nm, which corresponds to resonance tuning of 250 pm/V. This is one of the largest tuning efficiencies induced by fast carrier effect (depletion and accumulation) ever reported so far. To have an easy comparison with conventional silicon MZI modulator, such tuning efficiency corresponds to an equivalent  $V_{\pi}L$  of 0.18 V · cm. Although higher tuning efficiency can be achieved through heavy carrier injection in p - i - n diode structures [22,23], those devices suffer from the high energy consumption and low E-O modulation speed due to the lifetime of free carriers, which are not suitable for high speed modulators. The Q factor drops to 1850 due to the increased imaginary part of the permittivity as the voltage increases. The shift of the peak wavelength and the degradation of the

Q factor are plotted in Fig. 4(b). The imaginary part modulation of the optical permittivity, mainly from the In<sub>2</sub>O<sub>3</sub> layer, also increases the optical loss and reduces the peak transmission.

Figure 4(c) plots the extinction ratio (ER) spectra as a function of the applied bias. The maximum modulation is observed at 1545.46 nm. The ER at this wavelength as a function of the applied voltage is shown in Fig. 4(d). The flat band voltage of roughly 0 V is observed, which is due to the similar Fermi levels of In<sub>2</sub>O<sub>3</sub> and *p*-type silicon. An ER of 16 dB is achieved with a bias changing from 0 to -4 V. We also plot the peak transmission versus the applied voltage as shown in Fig. 4(d). With -4 V applied voltage, the peak transmission drops by 5.6 dB. Compared with the peak transmission drop, the imaginary part modulation of the optical permittivity roughly contributes to around 1/3 of the total ER. The leakage current of the device at -4 V is around  $10^{-14}$  A, which is at the noise level of our measurement equipment. This also means the static power consumption of the MOS capacitor is negligible. The driving voltage for 3 dB ER is reduced to less than 1 V, 12 times less than our previous work, which is compatible with CMOS driving circuits. We can estimate the energy consumption of the modulator by  $(CV^2/4)$  to be 3 fJ/bit. The driving voltage can be further reduced by decreasing the gate oxide layer thickness. For example, by decreasing the HfO<sub>2</sub> thickness to 5 nm, we can double the tuning efficiency to 500 pm/V while decrease the driving voltage to 0.5 V. If we can increase the Q factor to 5000, we can further decrease the driving voltage to 0.37 V, achieving an energy efficiency of 0.8 fJ/bit.

The speed of the photonic crystal nanocavity modulator is only limited by the resistor-capacitor (RC) time constant given the moderate Q factor below 5000. Considering the silicon doping level of our fabricated device,  $\sim 10^{17}$  cm<sup>-3</sup>, simulation shows a series resistance of  $\sim 1 \text{ M}\Omega$ , which yields a RC-delay limited speed of 0.12 GHz together with a capacitance of 13 fF. In the AC measurement of the nanocavity modulator, the rising time of the transmitted optical signal shows a good match with our simulation analysis of  $\sim 10^{-9}$  s. Unfortunately, a large falling time of  $\sim 10^{-6}$  s is observed, possibly due to the Schottky contact at the In<sub>2</sub>O<sub>3</sub>/Au interface. We will address this challenge according to the suggestion from [12]. The RF bandwidth can be increased to 2 GHz by simply increasing the silicon doping concentration to  $5 \times 10^{18}$  cm<sup>-3</sup>. According to 3D FDTD simulation [14], such a doping concentration will not limit the Q factor up to at least 5000. The additional insertion loss from the increased doping level can be estimated by the passive waveguide loss (0.017 dB/ $\mu$ m for 5 × 10<sup>18</sup> cm<sup>-3</sup> doping concentration [14]) and the photon lifetime of the nanocavity (~4 ps for Q factor of 5000), which equals to only  $\sim$ 1 dB. To further improve the performance, a slab photonic crystal cavity design and advanced doping technique [22] must be used. Then the series resistance can be reduced to less than 1 k $\Omega$  and the modulation bandwidth can be increased to over 12 GHz. High speed RF modulation will be implemented in our future design and characterization.

In summary, we demonstrate a low-voltage silicon photonic crystal nanocavity modulator with an ultrashort  $In_2O_3$  electrical gate of only 350 nm in length, showing a large resonance tuning efficiency of 250 pm/V and an average modulation

gate to achieve 3 dB modulation, which corresponds to an energy efficiency of 3 fJ/bit. The performance of the device can be further improved to less than 0.5 V operating voltage and sub-1 fJ/bit energy consumption, offering the possibility to be directly driven by CMOS logic gates. These combined merits prove the great potential of the TCO-gated silicon nano-cavity modulator for future CMOS driven integrated photonic interconnect systems.

**Funding.** Air Force Office of Scientific Research (AFOSR) (FA9550-17-1-0071).

**Acknowledgment.** This work is supported by the AFOSR Multidisciplinary Research Program of the University Research Initiative (MURI) under the guidance of Dr. Gernot Pomrenke.

## REFERENCES

- 1. P. J. Winzer and D. T. Neilson, J. Lightwave Technol. 35, 1099 (2017).

- 2. H. Iwai, Microelectron. Eng. 86, 1520 (2009).

- W. M. Green, M. J. Rooks, L. Sekaric, and Y. A. Vlasov, Opt. Express 15, 17106 (2007).

- J. Ding, H. Chen, L. Yang, L. Zhang, R. Ji, Y. Tian, W. Zhu, Y. Lu, P. Zhou, R. Min, and M. Yu, Opt. Express 20, 7081 (2012).

- 5. Q. Xu, B. Schmidt, S. Pradhan, and M. Lipson, Nature **435**, 325 (2005).

- X. Xiao, X. Li, H. Xu, Y. Hu, K. Xiong, Z. Li, T. Chu, J. Yu, and Y. Yu, IEEE Photon. Technol. Lett. 24, 1712 (2012).

- E. Timurdogan, C. M. Sorace-Agaskar, J. Sun, E. S. Hosseini, A. Biberman, and M. R. Watts, Nat. Commun. 5, 4008 (2014).

- 8. L. Zhou and A. W. Poon, Opt. Express 14, 6851 (2006).

- M. Liu, X. Yin, E. Ulin-Avila, B. Geng, T. Zentgraf, L. Ju, F. Wang, and X. Zhang, Nature 474, 64 (2011).

- A. Majumdar, J. Kim, J. Vuckovic, and F. Wang, Nano Lett. **13**, 515 (2013).

- V. J. Sorger, N. D. Lanzillotti-Kimura, R. M. Ma, and X. Zhang, Nanophotonics 1, 17 (2012).

- M. G. Wood, S. Campione, S. Parameswaran, T. S. Luk, J. R. Wendt, D. K. Serkland, and G. A. Keeler, Optica 5, 233 (2018).

- H. W. Lee, G. Papadakis, S. P. Burgos, K. Chander, A. Kriesch, R. Pala, U. Peschel, and H. A. Atwater, Nano Lett. 14, 6463 (2014).

- 14. E. Li, Q. Gao, R. T. Chen, and A. X. Wang, Nano Lett. 18, 1075 (2018).

- R. M. Briggs, I. M. Pryce, and H. A. Atwater, Opt. Express 18, 11192 (2010).

- E. Feigenbaum, K. Diest, and H. A. Atwater, Nano Lett. 10, 2111 (2010).

- A. P. Vasudev, J. H. Kang, J. Park, X. Liu, and M. L. Brongersma, Opt. Express 21, 26387 (2013).

- 18. Q. Quan and M. Loncar, Opt. Express 19, 18529 (2011).

- Y. Akahane, T. Asano, B. S. Song, and S. Noda, Nature 425, 944 (2003).

- B. Gayral, J. M. Gérard, A. Lemaitre, C. Dupuis, L. Manin, and J. L. Pelouard, Appl. Phys. Lett. 75, 1908 (1999).

- A. Shakoor, K. Nozaki, E. Kuramochi, K. Nishiguchi, A. Shinya, and M. Notomi, Opt. Express 22, 28623 (2014).

- S. Meister, H. Rhee, A. Al-Saadi, B. A. Franke, S. Kupijai, C. Theiss, L. Zimmermann, B. Tillack, H. H. Richter, H. Tian, and D. Stolarek, Opt. Express 21, 16210 (2013).

- M. G. Wood, J. R. Burr, and R. M. Reano, Opt. Express 24, 23481 (2016).